PDN — power distribution network или целостность питания.

Z target — Граница максимального значения импеданса между источником питания и потребителем (ножки микросхем) в неком частотном диапазоне. Понятие применяется для анализа целостности питания.

В разделе «Z-taeget», почему это может быть важно», рассказывается немного про принципы PDN анализа, она может быть полезна для понимания критичности или не критичности эффекта анти-резонанса.

Z-taeget, почему это может быть важно

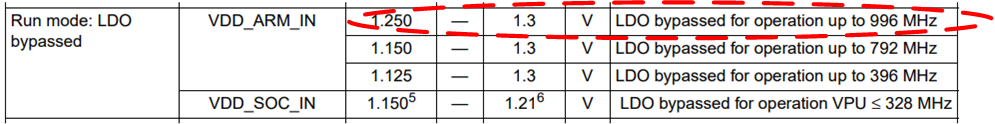

Прежде чем разобраться с явлением анти-резонанса, разберёмся где его важно учитывать. Если посмотреть на схему питания FPGA/Процессора, в глаза бросается обилие питающих напряжений среди которых есть напряжение питания ядра. Как правило, это самый низковольтный порт питания с высоким потреблением. Теперь представьте, что допуски по этому напряжению +/- 2%. Для типичных 3.3V звучит не очень жестковато, ведь допустимый размах пульсаций ниже чем 0.12V, достичь можно. Только в случае с процессором мы имеем дело не с 3.3V, а к примеру с 1.275V. И те самые +/- 2% это 25mV в одну сторону!

Вот пример из datasheet на i.mx6

И всё это при токах 1-10А (на самом деле диапазон гораздо шире, всё зависит от конкретной микросхемы).

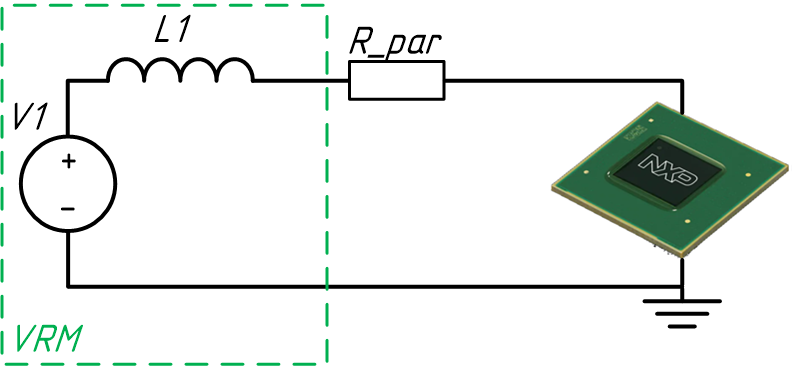

Ок! Допустим, применим импульсный источник питания с точными резисторами в обратной связи и обязательно попадём в нужный диапазон напряжений. Попасть в нужный диапазон не так сложно, хоть он и является очень узким. Сложности наступают в другом… Для того чтобы понять нарисуем эквивалентную схему источника питания и потребителя.

В схеме: V1 — DC/DC источник питания, R_par — паразитное сопротивление между выходными конденсаторами источника питания и ножками питания процессора.

Тут уже интереснее… Допустим у нас потребляемый ток от V1 = 3А. При R_par = 20mOhm падение напряжения составит 60mV!!! Это превышает допустимый порог в допустимые 2%(25mV при условии что напряжение в середине допустимого диапазона). Отсюда уже можно сделать вывод: заливать полигон питания абы как уже не получится. Нужно крайне внимательно подходить к проектированию шин питания.

Предположим мы постарались и нам удалось достичь R_par = 7mOhm. При новом значении падение напряжения получается 21mV и в целом пролазим в допустимый диапазон. Но проблема в том, что на этапе проектирования не всегда можно учесть все нюансы и полученная цифра 7mOhm может не совпадать с реальностью.

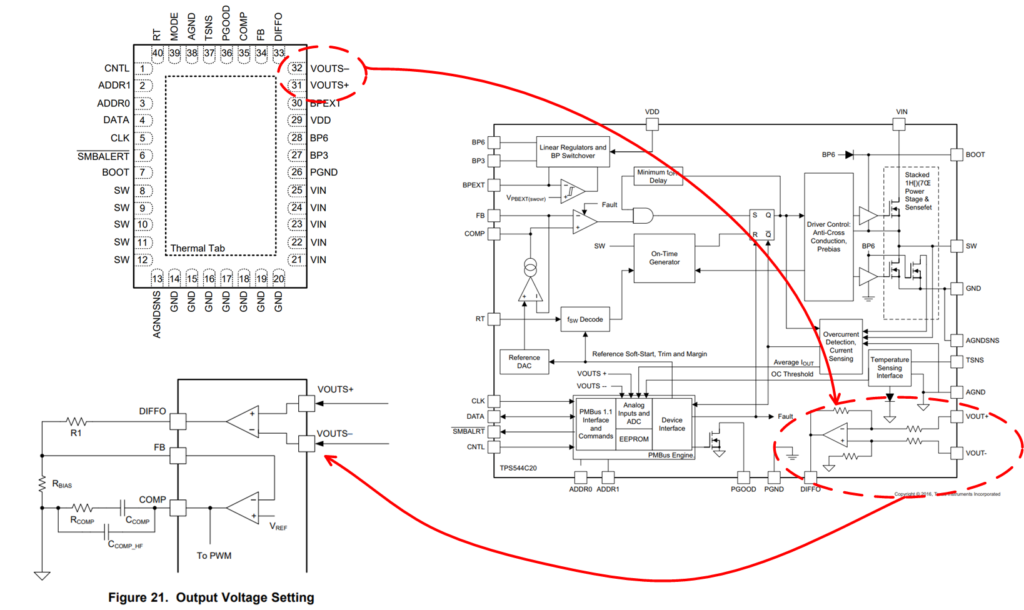

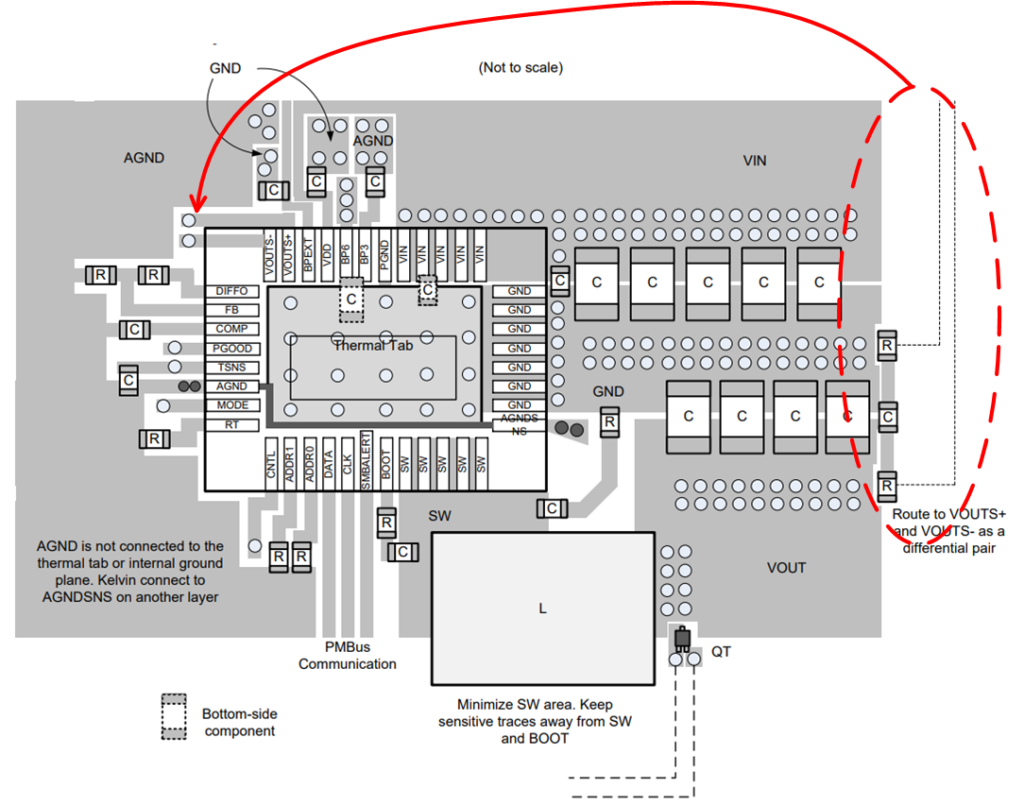

Частично данную проблему можно решить на уровне схемотехники заложив микросхему DC/DC с «Differential Remote Sense». В преобразователь встроен дифференциальный усилитель ошибки, который учитывает падение напряжения на полном сопротивлении пути (R_drop — полигон питания + возвратный ток по земле).

Вот так это выглядит при трассировке:

Т.к. в примере предполагается, что нагрузка подключается в непосредственной близости к выходным конденсаторам, то обратная связь взята оттуда. На практике её нужно брать как можно ближе к питающим ножкам потребителя, это позволит скомпенсировать падение напряжения на паразитном сопротивлении.

С постоянной составляющей потребления всё понятно. Что делать с переменной составляющей? Ведь мы питаем не резистивную нагрузку, а сложную микросхему с огромным количеством коммутаций ключей внутри. Если вернуться к нашей эквивалентной схеме с V1 и R_par, то для анализа целостности питания её надо усовершенствовать, добавив индуктивность.

Остановимся немного и рассмотрим что это за VRM и что за индуктивность L1. VRM это из области power integaty, расшифровывается как Voltageregulator module. При моделировании/расчёте целостности питания есть две основные сущности — это потребитель и источник. Как можно догадаться VRM это источник, который нужно представить как простую модель. Представить VRM в виде идеального источника напряжения будет неправильно, так как каким бы сильным импульсное потребление тока не было, напряжение не просядет (тут мы не учитываем паразитные параметры вносимые корпусами компонентов). Хотя в реальной жизни мы знаем что это не так.

В модели с идеальным источником напряжения мало смысла для анализа Z target, поскольку на всех анализируемых частотах весь потребляемый ток будет протекать через источник V1 и при импульсе тока никакой просадки напряжения нет, в реальной жизни это не так, и поэтому модель с идеальным источником напряжения не подходит для этого анализа.

Другое дело, модель с индуктивностью, индуктивность не даёт переменному току идти через источник V1, он замыкается через конденсатор С1 из за этого появляются колебания напряжения. Это естественно ближе к реальной жизни!

Однако я хочу уточнить 2 момента. Момент 1: модель с индуктивностью всё равно является достаточно примитивной и существуют более продвинутые и точные модели VRM. Момент 2: схема с идеальным источником напряжения имеет право на жизнь, например для IR drop анализа. Эти оба момента достаточно обширны и возможно будут рассмотрены в отдельных статьях.

Теперь немного поподробнее про индуктивность L1 в составе VRM. Сразу отвечу, это НЕ индуктивность, которая используется в импульсном источнике питания. Дело в том что в источниках питания есть время задержки реакции на возмущение, преобразователю нужно некоторое время, чтобы скомпенсировать напряжение на усилителе ошибки в цепи обратной связи. Из за этого происходят проседания и всплески напряжения при импульсной нагрузке. Добавляя индуктивность L1 в модель VRM мы искусственно вносим задержку которая на самом деле вызвана особенностями работы обратной связи в преобразователе напряжения. Здесь не будем касаться тонкостей выбора значения индуктивности L1, но обычно это 10-50нГн.

Теперь становится очевидно, что на одном преобразователе (далее VRM) не возможно удовлетворить требования по datasheet для питания ядра, поэтому нужно добавлять некоторое количество конденсаторов. Но какое именно и какого номинала? За частую нельзя обойтись стандартными 100nF на ножку. И вот тут мы в плотную подошли к постановке задач для частотного анализа Z target.

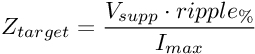

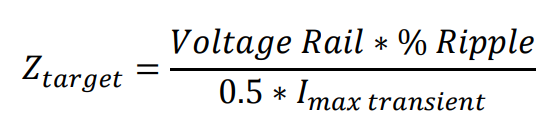

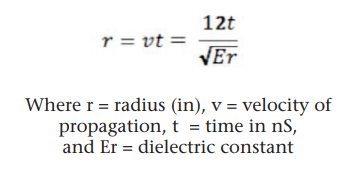

Представим что мы знаем максимальный ток по шине питания I_max, максимальный % отклонения напряжения ripple(%). Мы ведь можем найти по закону ома верхний предел сопротивления для I_max, чтобы не выйти за диапазон напряжения, который взят из документации (в нашем случае ripple(%)). V_supp — номинальное напряжение питания.

Хочу отметить, что это наиболее консервативный подход, который загоняет разработчика печатной платы в жёсткие рамки. В чём консервативность? Мы говорим про частотную область, другими словами от 1Hz до условных 100MHz. По нашей формуле, получается, что как будто на каждой частоте будет потребляться один и тот же ток I_max. Однако это не так! Например в документах TI можно встретить ослабляющий коэффициент 0.5:

У производителей FPGA, можно скачать xls файл, в котором вбив свои параметры, скрипт сам выдаст необходимые рекомендации по Z_target. Если я не ошибаюсь, тоже самое можно сделать и через IDE для FPGA, которая на основе твоей прошивки FPGA, даст рекомендации по Z_target и точные прогнозы о потреблении по каждой шине.

Полученный импеданс должен соблюдаться от VRM до нагрузки вплоть до некой максимальной частоты F_max (ещё называют эффективной частотой). Что эта за частота? Тут так же как и с Z_target, есть консервативный подход и более мягкий. Более мягкий как правило заключается в приравнивание F_max приблизительно к 10-20MHz. Консервативный, в литературе как правило его и придерживаются, заключается в оценки частоты F_max по корпусу паразитным параметрам корпусу микросхемы.

Вот пример. Допустим, по расчётам Z_target = 50 mOhm. А ножка микросхемы имеет индуктивность 1nH. Как правило у микросхем не одна ножка питания, а скажем 10. Тогда 10 индуктивностей в параллель дают эквивалентную индуктивность 0.1nH. Теперь нам нужно найти ту частоту, на которой эквивалентный импеданс ножек микросхемы будет равен Z_target. Как мы знаем импеданс индуктивности это:

От сюда находим f = 79MHz. Именно эту частоту можно назвать максимальной. Другими словами это объясняется так: мы можем добиться импеданса шины питания ниже чем Z_target на частотах и выше чем F_max. Но какой в этом смысл, если на преграде к кристаллу стоит ножка микросхемы, у которой импеданс в несколько раз выше, чем наша шина питания.

Итак, подход по определению f_max : максимальная граница частот это та, за пределами которой, добавление новых конденсаторов уже не улучшает общую картину импеданса.

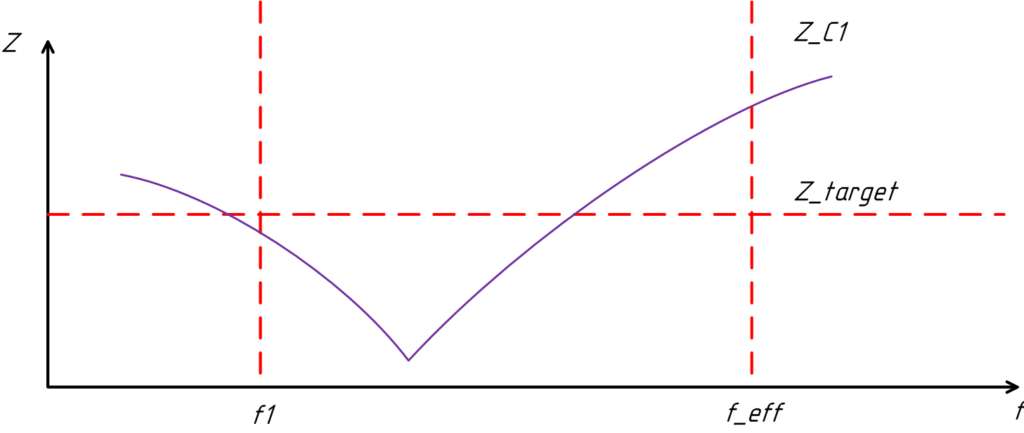

Ну и в конце этого раздела, визуализация ваше сказанного, взято из мануалов Altera.

Толстым красным выделен результирующий импеданс. Синий Z_target. Остальные тонкие линии это конденсаторы. Видно, что Z_eff < Z_target добиваются множеством различных конденсаторов у которых разная собственная резонансная частота. Так же обратите внимание на Z_vrm, который начинает резко расти от 40kHz, говорит о том, что на импульсную нагрузку выше 40kHz обратная связь преобразователей уже отрабатывает неэффективно.

Анти-резонанс параллельных конденсаторов.

Когда речь идёт о конденсаторах мы привыкли слышать о собственной резонансной частоте. Напомню, эта та частота где импеданс конденсатора имеет наименьшее значение, которое равно ESR. Такая зависимость импеданса от частоты для единичного конденсатора получается из-за следующей эквивалентной схемы:

Если построить зависимость от частоты, получим приблизительно следующие:

Собственно сам анти-резонанс тоже резонанс, только произойти он может, когда в наличии не один конденсатор, а несколько разных в параллель.

Раз речь идёт о параллельных конденсаторах, то какой же может быть резонанс? Для параллельного резонанса нужна как и емкость, так и индуктивность. Но если посмотреть на картинку выше, видно что, конденсатор может быть как емкостью (синяя область), так и индуктивностью (красная область).

Теперь вспомним условия возникновения резонанса. Если Q (добротность) больше 1. Добротность параллельного RLC контура находится как:

Здесь R является эквивалентной нагрузкой(микросхема).

Теперь представим, перед нами стоит задача, спроектировать шину питания, у которой Z_target будет ниже некой константы.

Ставим 1 конденсатор и смотрим.

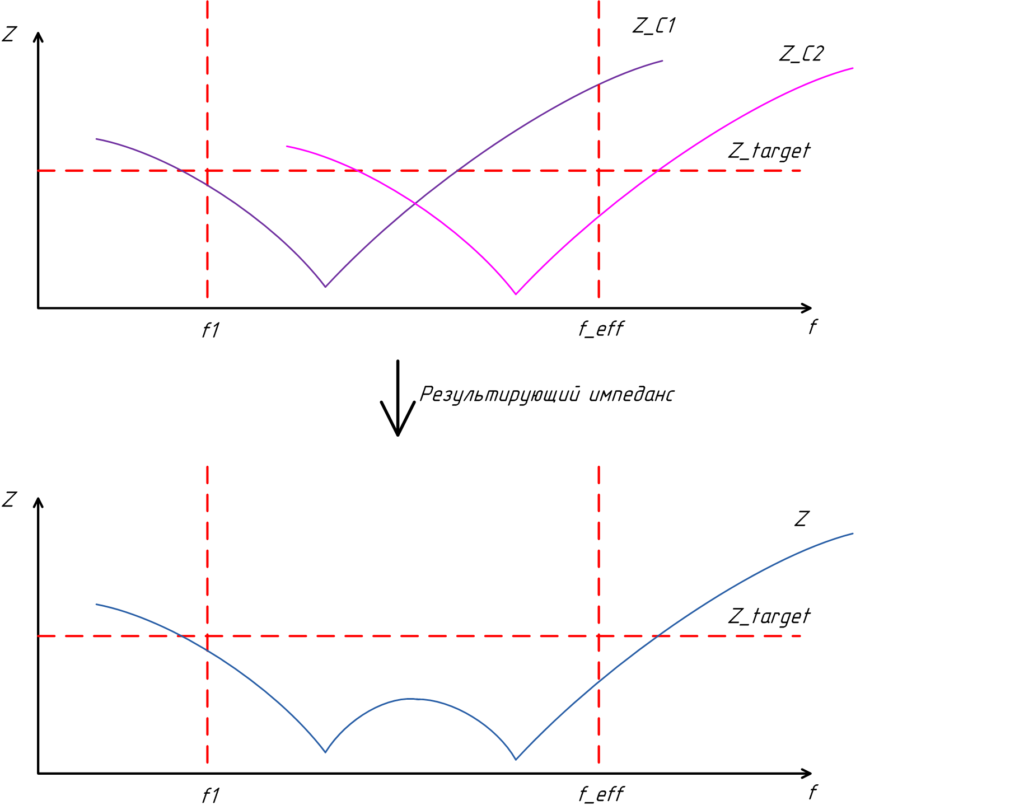

Одного конденсатора С1 будет маловато. Ну что ж… Поставим ещё один, но с другим номиналом. Вот что мы ожидаем увидеть.

Вроде всё отлично! Но тут всё как с знаменитым мемом ожидание — реальность.

Так же и у нас. Реальность будет выглядеть примерно так:

Чтобы понять, почему так происходит, ещё раз взглянем на импедансы конденсаторов по отдельности.

Отчётливо виден момент, когда Z_C2 ведёт себя как емкость, а Z_C1 как индуктивность. Чем не резонансный контур?

Нужно быть крайне внимательным при подключении конденсаторов разных номиналов. Как избежать всего этого? Например, в этой статье рекомендуют ставить конденсаторы в параллель с номиналом, разница у которых не отличается в более чем в 10 раз. Для примера возьмём два разных случая: 1) большая разница в номиналах, 2) маленькая разница в номиналах.

Случай 1.

Случай 2.

Как вывод из этих двух схем можно отметить: там где важен Z_target, желательно провести анализ схемы, иначе велик риск нарваться на не очевидные артефакты.

Ограничение.

Если речь идёт об общей шине, где много конденсаторов. Возникает вопрос, а все ли их учитывать?

Ответ: Нет! Резонанс это такой же физический процесс как и прохождение сигнала по проводнику. По сути это перетекание токов из одного реактивного элемента в другой. Мы знаем, что ток в печатной плате распространяется с конечной скоростью. Зная частоту резонанса и скорость распространения, можно найти область охвата.

Вопрос радиуса чуть подробнее рассмотрен тут. Но как правило, те шины для которых может быть важен эффект анти-резонанса, не являются общими.

1 Reply to “Немного PDN и анти-резонанс параллельных конденсаторов.”

Comments are closed.